AMD Driver Hints Flagship RDNA 3 GPU Is A Burly Beast With 6 MCDs And A Huge Cache

The release of "Big Navi" changed all that, but it's looking like NVIDIA's next generation of GPUs will be even bigger and more beastly than Ampere despite being named after a high-class lady. According to rumors, AMD plans to respond in kind, with an even bigger Navi GPU that aims to go head to head against Lady Lovelace.

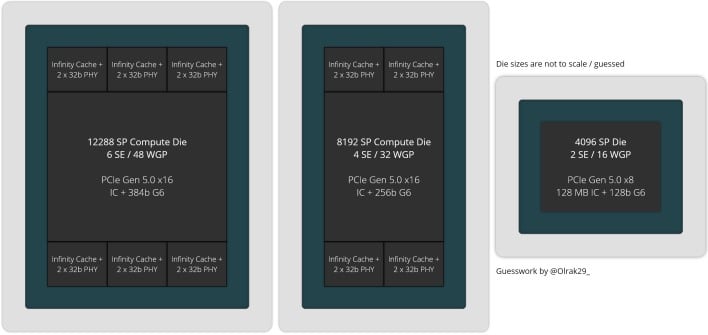

The biggest GPU in the Navi 3x family will probably be known as Navi 31—or rather, probably is already known that way within AMD. Expectations for Navi 31 were extremely high, but have been tempered slightly with updated information a couple of months ago. Shortly after that, it came out that Navi 31 may actually expand the memory bus by 50% compared to Navi 21. That's the GPU used in the RX 6800 and all larger released Radeons.

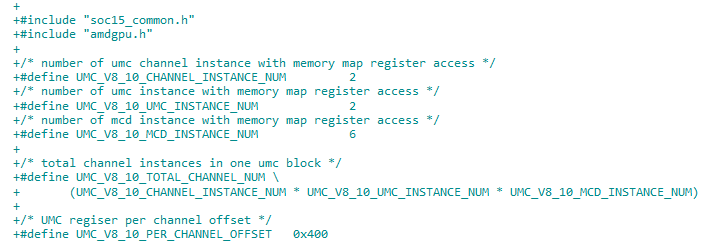

If you're wondering what an MCD is, it's a separate die that includes cache, a GDDR6 memory interface, and possibly external I/O for an RDNA 3 GPU. If you've been really out of the loop lately, AMD's confirmed that its next-gen Radeons will be built using chiplets like its Ryzen CPUs.

Many people have envisioned a GPU with multiple chiplets being difficult to build owing to the challenge of splitting up a graphics workload across discrete processors, but it's seeming more likely that AMD will remain using a single GPU compute chiplet with multiple cache, memory, and I/O chiplets. That's a much easier configuration to manage, even if it doesn't give the same benefits for manufacturing as a multi-die GPU.

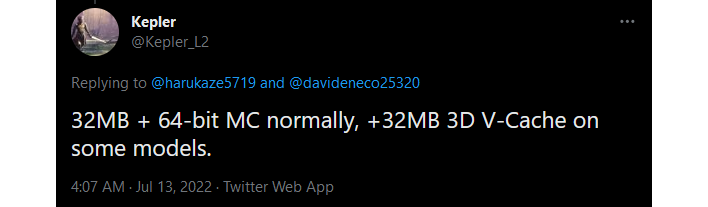

This information was pointed out by Kepler on Twitter, who also had some interesting observations to make regarding the Infinity Cache allotment on RDNA 3 GPUs. As with RDNA 2, it seems to be approximately 16MB of Infinity Cache per 32-bit memory channel, at least at a maximum. However, Kepler seems to think that AMD is able to double that allotment using 3D V-Cache. By stacking a second 32 MB SRAM die on top of each MCD, the biggest Navi 3x parts could end up with as much as 384 MB of Infinity Cache.