AMD Patent Outlines big.LITTLE-Style Architecture For Future Hybrid CPU Designs

AMD has filed a patent with the United States Patent and Trademark Office (USPTO) describing a hybrid processor architecture that is drawing parallels to ARM's big.LITTLE design philosophy. They are very different architectures, but the concept of pairing more powerful cores for heavy lifting with power efficient cores for less intensive chores is somewhat similar.

This type of approach works well in the mobile space where battery life considerations factor into the equation. AMD acknowledges this in its patent application.

"Increasing battery life is important to users of mobile devices that operate on battery power, sometimes for extended periods of time. Accordingly, there is a need for efficient, low power systems that deliver scalable computational capacity with diminishing energy cost," AMD states.

Battery stamina obviously does not matter for a typical desktop PC, but perhaps this kind of design could work well in a laptop. It is not entirely clear what form factors AMD has in mind, only that it is at least researching hybrid CPU designs. As spotted by Twitter user Underfox, this is laid out in the patent application, which was actually filed nearly two years ago.

Here is the abstract...

A heterogeneous process system includes a first processor implementing an instruction set architecture (ISA) including a set of ISA features and configured to support a first subset of the set of ISA features. The heterogeneous processor system also includes a second processor implementing the ISA including the set of ISA features and configured to support a second subset of the set of ISA features, wherein the first subset and the second subset of the set of ISA features are different from each other. When the first subset includes an entirety of the set of ISA features, the lower-feature second processor is configured to execute an instruction thread by consuming less power and with lower performance than the first processor.

AMD notes in its patent application that reducing power in high performance CPUs is a difficult task because of the various techniques involved aimed at achieving high performance, including complex instructions, deep pipelining, superscaler capabilities, and aggressive speculative operations. This is where the hybrid approach would come into play.

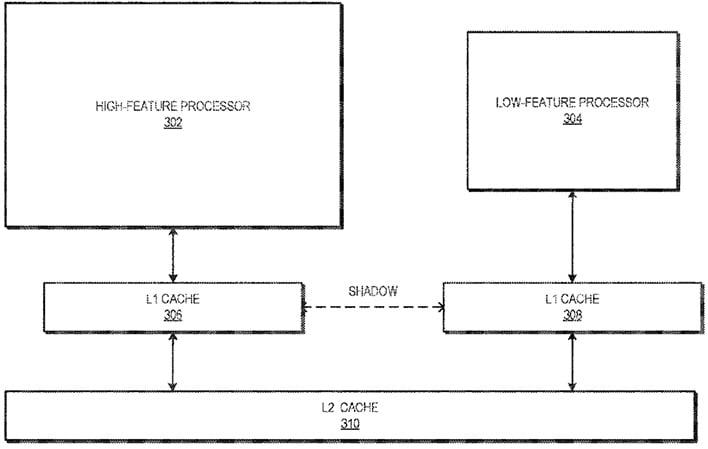

Tasks could be switched from high to low power cores, depending on the need, to reduce power consumption. AMD envisions this kind of design being implementing with or without a hierarchy of cache levels, with a cache controller in at least one of the designs. This design would also be capable of moving instructions threads back and forth between the high and low power cores, as needed.

It's interesting to discover that AMD has put some research into this approach, given that Intel appears to also be adopting a hybrid design with Alder Lake. Of course, patented technologies do not necessarily manifest into shipping products. At the very least, though, this is something AMD has considered.