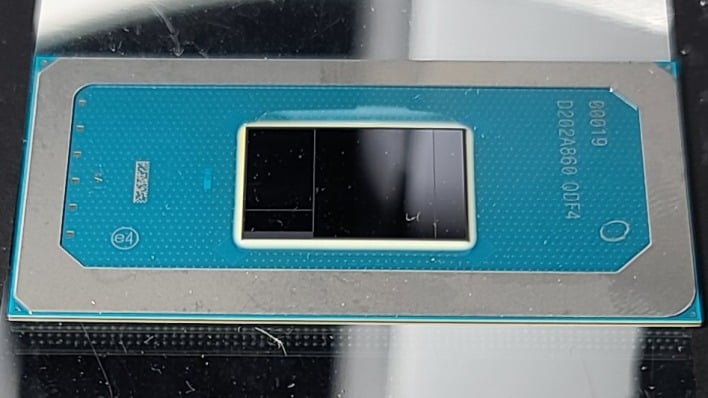

Linux Driver Patch Reveals L4 Cache For Intel 14th-Gen Meteor Lake Processors

Traditionally, the integrated graphics on Intel's CPUs have been able to make use of the CPU's last-level cache (LLC) to help with the most latency- and bandwidth-sensitive graphics operations. That's not going to be possible—or at least practical—with Intel's next-generation processors because of their tiled nature. The CPU L3 cache will reside on the compute tile, and to access it, the GPU would have to cross the base tile.

Not having any sort of cache at all would be miserable for the GPU's performance. Even discrete GPUs have considerable caches for rapid data mangling. While the Arc Alchemist-based GPU tile for Meteor Lake surely has some L1 cache on-die, it'll need a larger cache for good performance. Fortunately, thanks to a leak from Intel's Fei Yang, we know that the Blue team's 14th-gen CPUs will include a L4 cache for this reason.

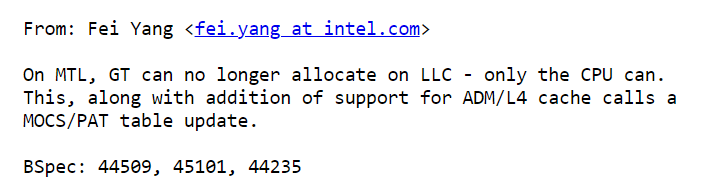

Source: intel-gfx mailing list.

Replying to a post on the intel-gfx mailing list, Yang remarked that the "GT"—that refers to the integrated graphics on Intel—"can no longer allocate on LLC - only the CPU can." He goes on to say that this change, "along with addition of support for ADM/L4 cache" requires updates to the Linux graphics driver.

We have no idea what "ADM" stands for; some reasonable guesses are "All Device Memory" or "Arc Discrete Module". "L4 cache" is clear enough, though. This leak comes to us by way of Japanese-language hardware blog Coelacanth's Dream, where the Coelacanth ponders the function and location of the L4 cache. He mentions the last time Intel's processors had an L4 cache, which was with the Crystal Well eDRAM package on certain older CPUs.

It will be interesting to see whether these conjectures are accurate, as well as whether Intel will use the size of the L4 cache as a means of segmenting Meteor Lake processors. It will also be fascinating to see what effects it has on processor performance, again both CPU and GPU. You can bet that we'll be looking into this once we have 14th-gen silicon in hand.