Intel And Synopsys Demo 32GT/sec PCIe 5.0 Interoperability With Next-Gen Sapphire Rapids Xeon CPUs

To that end, Intel is already looking towards PCIe 5.0, and this week announced that it has worked with Synopsys to demonstrate operability with its next-generation Xeon Scalable processors, aka Sapphire Rapids. For the demonstration, Intel made use of the Synopsys DesignWare controller and physical interface (PHY). The goal with this early demonstration is to help deliver a smooth development process for PCIe 5.0 products and ensure wide compatibility with Intel platforms going forward, both for the enterprise and consumer markets.

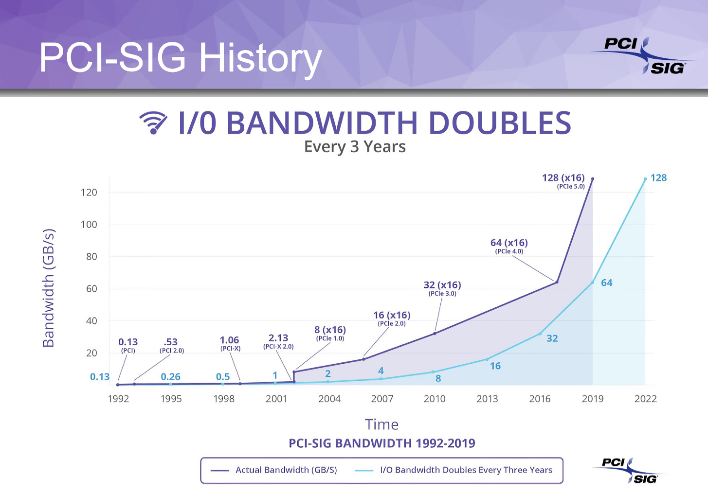

During the demonstration, the two companies were able to achieve a 32GT/sec link, which is the maximum throughput for the PCIe 5.0 spec. This is double the throughput of the current-generation PCIe 4.0 interface. This increased speed will result in performance benefits for a wide variety of application including artificial intelligence, machine learning, visual computing, storage, and networking (among others).

"The growth of high-performance computing applications converged with AI workloads requires innovative data connectivity and processing technologies that deliver low latency and fast speeds," said Jim Pappas, Intel Director of Technology Initiatives. "We are pleased to collaborate with Synopsys, a leading provider of PCIe IP, to enable the ecosystem and ensure the widely adopted DesignWare IP for PCI Express 5.0 is interoperable with our future CPUs in order to enable the billions of PCIe-enabled products in the market."

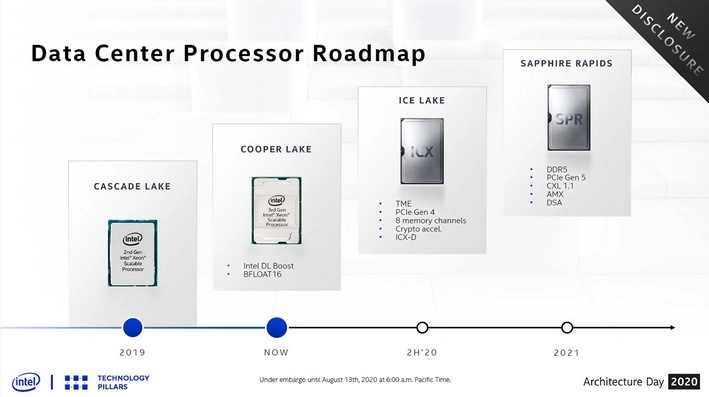

Intel's fourth generation Sapphire Rapids server Xeon Scalable processors are built on an enhanced 10nm SuperFin process node and are set to arrive in 2021 with support for DDR5 memory and the CXL 1.1 protocol. And interestingly enough, although PCIe 5.0 devices should be making waves in 2021, PCI-SIG is already paving the way for the PCIe 6.0 spec to be released the same year, once again doubling data rates to 64GT/sec.