Intel Is Making Big Changes To The x86 ISA With APX And AVX10 Extensions

Regular readers will recall that we wrote about Intel's X86S proposal awhile back. That was merely in the concept stages, but it's an idea to shed a lot of the legacy cruft from x86-compatible processors. It looks like Intel's engineers aren't done fiddling around in the instruction set, though, because the company's just announced two big changes to x86 for future processors: Advanced Performance Extensions (APX) and the unified AVX10.

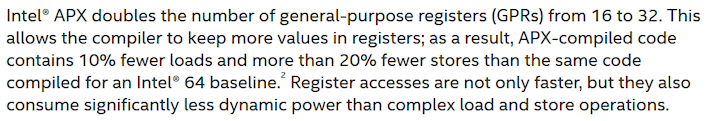

We'll talk about APX first, because there's less to say about it. APX is what Intel is calling an extension to the x86 ISA that primarily doubles the number of general-purpose registers (GPRs) from 16 to 32. If you're not up to snuff on your hardware lingo, a "register" is a very small space within the CPU that stores the data the processor is actively working on at any given time. In a sense, this is sort of like doubling the RAM on a CPU in that it reduces accesses to slower storage—just that in this case, the "slower storage" is CPU cache.

APX also does a lot of other things that won't mean much to anyone that isn't a developer—and a low-level programmer, at that. The extension adds three-operand instruction formats, meaning that you can store the result of an operation in a third register instead of overwriting a previous value. (Looking kinda RISC-y there, Intel.) Furthermore, there are optimizations to register state save/restore operations that save on die area by re-using the space originally marked out for Intel's MPX extensions that were removed back in 2019.

Ultimately, APX will mean an increase in average instruction length, but a significant drop in number of instructions for a given block of code. It also could result—depending on the application—in a considerably-reduced amount of accesses to larger caches and main memory. Taken as a whole these changes should offer improved efficiency for CPUs using the new extensions, which has traditionally been a weak point of the x86 ISA.

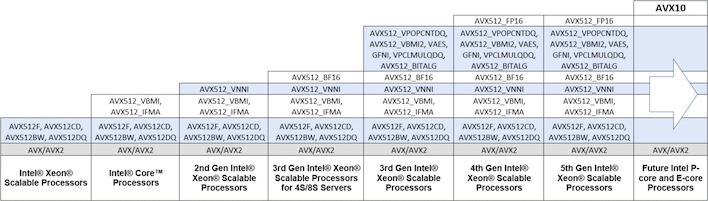

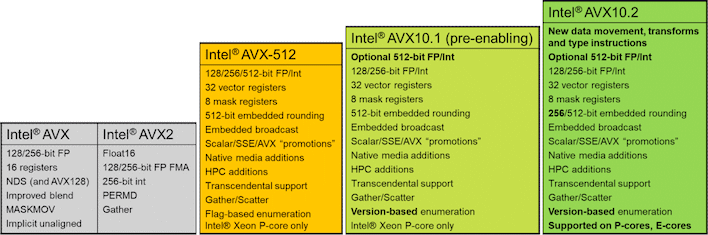

One of the stranger things to happen over at the house of x86 over the last decade has been the bizarre fragmentation of AVX-512 instructions. Originally introduced with the Xeon Phi processors, successive CPUs gained support for some instructions but not all, or added new instructions while missing support for some previous instructions. Rocket Lake had support for the instructions, but they were removed in Alder Lake and Raptor Lake due to issues related to the hybrid nature of those CPUs.

AVX-512 support was kind of a mess both due to poor versioning for the different variations as well as the requirement of including a massive 512-bit vector unit to support the features. This made it confusing to use for developers, and impractical for Intel to support on its low-power E-core architectures. Now, the company is making sweeping changes going forward that mean future CPUs will support basically all features of AVX-512, even if they are hybrid processors with P-cores and E-cores.

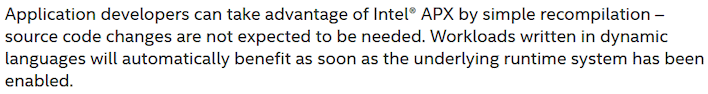

The new standard is simply called "Advanced Vector Extensions 10", or AVX10. AVX10 includes all of the instructions supported by previous AVX extensions, including the VNNI, bfloat16, FP16, and other groups. Arguably the most notable feature of AVX10 for developers is that it introduces a versioning approach to enumeration using CPUID flags.

There are three parts to the AVX10 CPUID: one that specifies support, one that lists the AVX10 version number, and then a third that enumerates the maximum vector width that the CPU in question supports. Since the AVX10 version number will be "inclusive and monotonically increasing", you can simply query the version number to know what extensions the CPU you're using supports.

Intel says AVX10 only requires re-compilation to improve performance.

AVX10 also introduces a converged version of AVX-512 with a maximum vector register length of 256 bits. What this means is that future hybrid processors will be able to support most AVX-512 instructions on both P-cores and E-cores, but thanks to the improved enumeration, it will also be possible to make use of 512-bit vectors on P-cores in the same processor. Good news for game emulator developers, at least.

Intel doesn't say exactly when the new AVX10 standard will debut, but says that when it does, it will be backward compatible with all of the Intel AVX-512 ISA available as of the Granite Rapids CPUs. The initial AVX10 version will be AVX10.1, or "AVX10 version 1", which won't include any new instructions; Intel says that it will serve as the transition base version from AVX-512 to AVX10. Afterward, AVX10 Version 2 will come along on P-cores and E-cores with enhanced support for 256-bit instruction forms for AVX-512 instructions.

As for APX, Intel doesn't say anything about when it will show up, nor about whether it's licensing the extensions to its longtime rival and partner AMD. There's a 1300-page architecture document [PDF] that we haven't dug through, but presumably it contains all the information that someone would need to implement the same changes in their CPUs. Hopefully we aren't entering a new era of mixed compatibility after the last 20 years of nearly-perfect interoperability between AMD and Intel CPUs.