Leaked Intel Sapphire Rapids 48-Core CPU With DDR5 Benchmarks Impress

Do you know about Sapphire Rapids? If you're someone who fiddles about with servers for their day job, you almost assuredly are waiting with bated breath for Intel's upcoming high-end processors. However, if you're Joe Gamer, or an overclocking enthusiast, you may not be as informed about the forthcoming datacenter darlings.

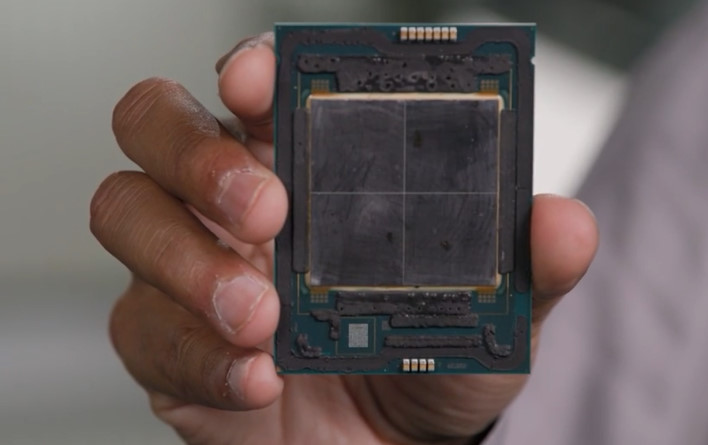

Built on Intel's "Intel 7" process (formerly known as 10nm Enhanced SuperFin), Sapphire Rapids is the codename for Intel's next Xeon Scalable processors. These will be the first Xeons to be built using a modular design with multiple "tiles," which would be called "chiplets" in AMD nomenclature. Intel will be using its EMIB packaging technology to ensure that the tiled chips appear to the system as monolithic CPUs, and that every part of every tile will have access to all of the resources on the other tiles.

Sapphire Rapids will use the essentially same Golden Cove CPU cores as in its current-generation Alder Lake desktop CPUs, although there will of course be significant modifications to suit the datacenter and HPC markets. Chief among those changes are new instruction sets, of course, including an FP16 adjunct to AVX-512 as well as the first implementation of Intel's Advanced Matrix Extensions, or AMX.

Each tile of a Sapphire Rapids CPU is itself a complete package with cores, cache, high-speed I/O, and a dual-channel DDR5 memory controller. So saying, a fully-equipped Sapphire Rapids Xeon would have four tiles, with "over 100 MB" of last-level cache and eight-channel DDR5 memory, as well as optional HBM on-package. Intel hasn't revealed the core count of a single tile, but earlier leaks suggested either 56 or as many as 80 cores in a single socket.

So that all sounds great on paper, but it's the performance that matters, right? Chinese leaker YuuKi_AnS (@yuuki_ans on Twitter) seems to have their hands on a 48-core Sapphire Rapids sample, and has put it through the wringer running numerous benchmarks: AIDA64 cache & memory results, V-RAY, Cinebench R20 and R23, and CPU-Z benchmarks. Let's have a look at the data.

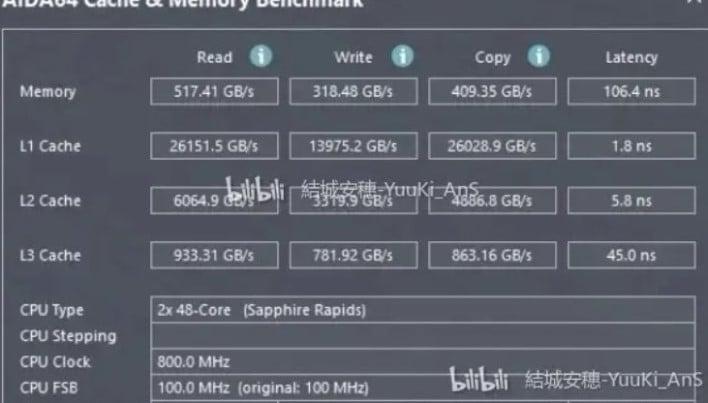

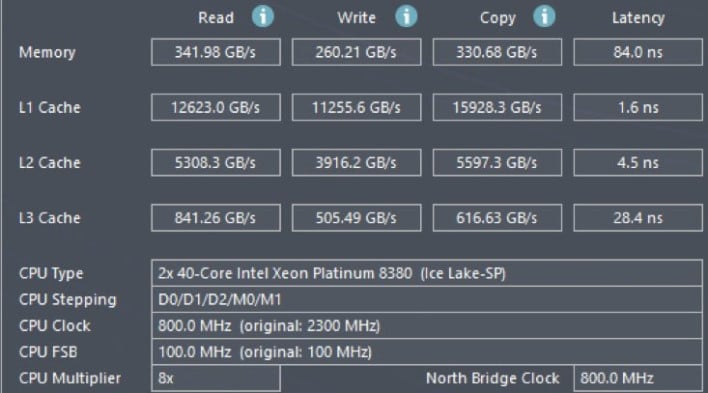

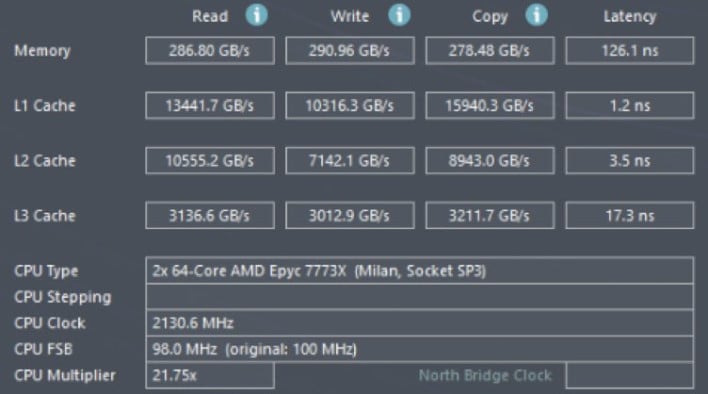

First up are the AIDA64 results, which you can see above compared against an Intel Xeon Platinum 8380 (Ice Lake-SP) machine as well as an AMD EPYC 7773X, which is a Milan-X chip with 3D V-cache. All three platforms have their strengths; the EPYC chip has by far the fastest cache among them, while the Ice Lake-SP processor enjoys the lowest memory latency. Sapphire Rapids' strength in this benchmark appears to be memory bandwidth. That's no particular surprise given the eight-channel DDR5 interface it enjoys, but it's nice to see the world make sense.

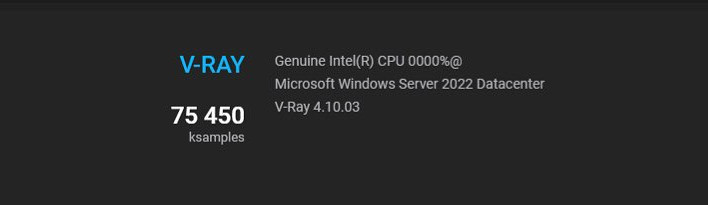

In V-Ray, the unreleased SPR Xeon cranked out a score of 75,450 kilo-samples. That already puts it ahead of the Xeon Platinum 8380 at 73008, while the EPYC chip lags behind at 69119, but YuuKi_AnS says that the Sapphire Rapids sample should be able to break through 80,000 with its final release, as the performance of the current version suffers from "bugs in BIOS and processor."

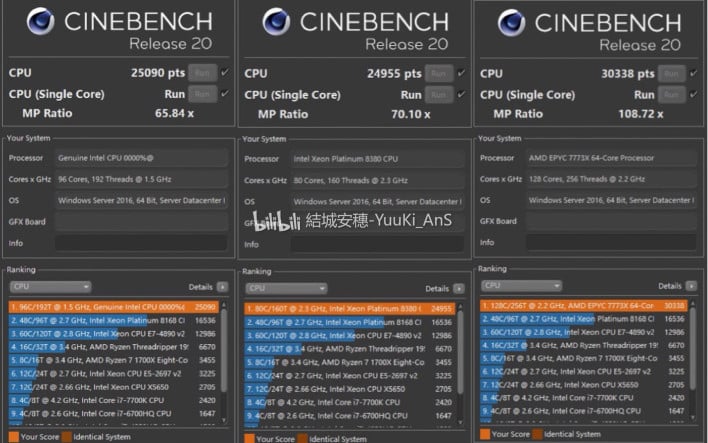

On the topic of Cinebench, YuuKi_AnS actually ran numerous benchmarks, but we'll just take a look at the Cinebench R20 numbers. Comparing across the three, at a glance it doesn't look great for the upcoming processor. If you look more carefully, though, the EPYC chip's epic performance comes from the fact that it has a full 128 cores—32 more than the dual-socket Sapphire Rapids machine, and 48 more than the Ice Lake box. The SPR chip barely edges out a win against the extant Xeons, but it's also running at just 1.5 GHz, likely owing to it being an early sample. In that context, the performance is actually stunning.

Finally, the CPU-Z data. In both the v17.01.64 version of the benchmark as well as the v19.01.64 version, the EPYC Milan-X chip destroys all comers, even in the single-threaded test. You can see the scores above. None of the single-threaded results are too impressive, but these massively multi-threaded processors run much lower clock rates than your typical desktop chip. It's the multi-threaded scores that are interesting, although admittedly the CPU-Z benchmark doesn't particularly correlate to anything.

YuuKi_AnS tried to run the AVX2 version of the CPU-Z benchmark, but it failed. The leaker comments that in the engineering sample chip that they have, "the AVX instruction set has not been completed." That apparently extends to AVX-512 and the aforementioned AMX instructions, as well, which the leaker calls "paid DLC items." In a later tweet, YuuKi_AnS clarifies that "some functions of HBM2e" as well as "AVX-512 and AMX" will "require payment" to use. This isn't the first we've heard of this kind of "hardware as a service," but Intel quietly dropped that idea a long time ago. Seeing it again is concerning—if the information is accurate.