Next-Generation FeDRAM Claims Are a Far Cry From Shipping Products

Information on a supposed DRAM breakthrough has been running hot across the wires, but the press release from Semiconductor Research Corporation (SRC) that's sparked techie interest across the Internet is a tad misleading. There's nothing factually incorrect regarding the group's achievement (at least not as far as we know), but the gap between where we are today and a commercially viable FeDRAM design is much, much wider than implied.

The PR states that the Semiconductor Research Corporation and Yale University have jointly developed "a new DRAM cell using ferroelectric layers that could significantly increase the technological and market competitiveness for DRAM technology."

"According to early findings, researchers have found a way to apply ferroelectric material to a DRAM cell, which eliminates the need for a storage capacitor found in conventional DRAM. Ferroelectric DRAM (FeDRAM) is a capacitor-less DRAM cell, with a cell structure very similar to a CMOS transistor, except that the gate dielectric is ferroelectric."

"Compared to the conventional DRAM cell, FeDRAM offers simpler cell structure, improved scalability, a smaller cell size, orders of magnitude longer retention time, lower power consumption and the possibility of storing multi-bits per cell. Storing many bits of information in a single DRAM cell has not been done and is found primarily only in flash memories."

We're actually going to ignore that bit about storing multiple bits of information in a single DRAM cell, as it's an entirely separate problem whose solution is even farther into the future if it ever happens at all. Instead, let's chat about RAM: Conventional DRAM, FRAM, and FeDRAM in particular.

Understanding RAM

If terms like "gate dielectric" and "ferroelectric" leave you gaping, this section should help clear things up. Traditional DRAM cells contain one transistor and one capacitor. The capacitor is literally what allows DRAM to function as memory; it retains an electrical charge once the cell is written to, and returns that pulse of information when it is requested. While critical, the capacitor is also something of an albatross. It significantly increases the size of the DRAM cell, it draws electricity, and it takes a measurable amount of time to apply a sufficient electrical field to cause the polarity of the transistor to switch from 0 to 1.

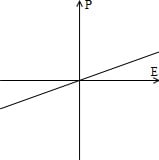

The DRAM cell is polarized linearly, which is to say that the polarity of the cell is proportional to the external electric field (diagram below.) This is called dielectric polarization.

That's how things work now. Ferroelectric materials don't exhibit a dilectric polarization, and that's what makes them so interesting. A ferrolectric cell is non-linear as shown below; polarization leaps (or drops) once a certain field strength is applied. Ferroelectric materials can switch polarity much more quickly than traditional dielectrics and they take less power to do it.

Problem is, none of the above is anything new. Research into Ferroelectric RAM (FRAM) began in the 1980s at NASA's Jet Propulsion Labratory; Texas Instruments, Fujitsu, and Ramtron currently ship products that incorporate small amounts of FRAM as a form of non-volatile storage. FRAM is also sometimes referred to as FeRAM, which could cause confusion. SRC's FeDRAM is a volatile memory that could one day hypothetically replace traditional DRAM; FRAM is a non-volatile technology that would theoretically compete with flash if certain obstacles were overcome.

The Capacitor Conundrum

It's critically important to distinguish between FRAM and what Semiconductor Research Corporation is calling FeDRAM. FRAM is a low-density, non-volatile storage medium that's capable of performance levels that leave conventional flash memory sucking wind. It's also extremely durable; FRAM can withstand an effectively infinite number of read/write cycles. FRAM exploits the characteristics of ferroelectric materials to perform the way it does, but FRAM cells do contain a capacitor.

SRC's FeDRAM doesn't. In theory, this opens the door for signficantly denser DRAM cells, easier scaling, and lower latency memory, all while reducing DRAM power consumption. Congratulations to the organization and its Yale partnership for successfully building a single FEDRAM cell, but that cell holds just one bit worth of data. Care to do the math on how many bits are in 1GB of memory?

Even if you can't completely understand the diagram, it's easy to see how simple and small the FEDRAM cell is compared to the more traditional trench and deep trench DRAM cells.

When the PR states that researchers "believe that with SRC support and collaboration with other SRC member companies, FeDRAM will be ready to transfer to the industry for production in the foreseeable future," they're blowing smoke. In reality, FEDRAM is one of a number of hypothetical "next-generation" memory techniques that may or may not ever be able to deliver on their initial promise. AMD has sunk $25 million into Innovative Silicon and its Z-RAM technology that doesn't actually work yet, Intel has backed PRAM, and there's any number of other approaches, from carbon nanotube-based NRAM to magnetoresistive memory (MRAM) to Racetrack memory (currently being researched at IBM).

SRC's accomplishment takes us one baby step closer to a potential new way to build memory at some point in the future. Whether or not that's the "forseeable" future depends entirely on how far down the road you want to look. Personally, I'm not holding my breath. Despite promising advances, none of the next-generation technologies currently being researched is ready to supplant existing DDR manufacturing methods.

Special thanks to Michael Schuette of Lost Circuits.