AMD Radeon RX 7900 XT Tipped For 24GB Of GDDR6 And 384-Bit Memory Bus

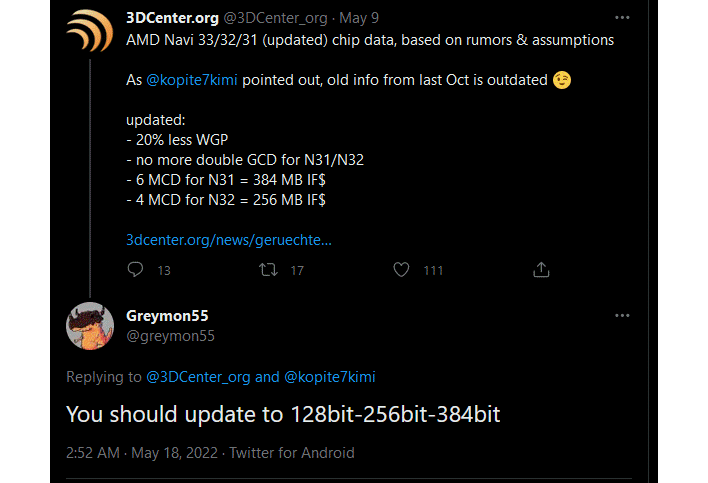

The latest leaks come from the usual Twitter suspects for pre-release GPU info, kopite7kimi and Greymon55. Specifically, kopite7kimi has noted that the information from last October is outdated and refers to older plans that AMD has since revised. Meanwhile, Greymon55 has some deets on the memory interfaces of the incoming higher-end Radeon parts.

See, microprocessor manufacturing isn't necessarily intuitive in the way costs scale. Simply put, the most expensive thing is die area—the bigger your die, the fewer chips you can get out of a single wafer, and the less chips you'll get that are fully-working.

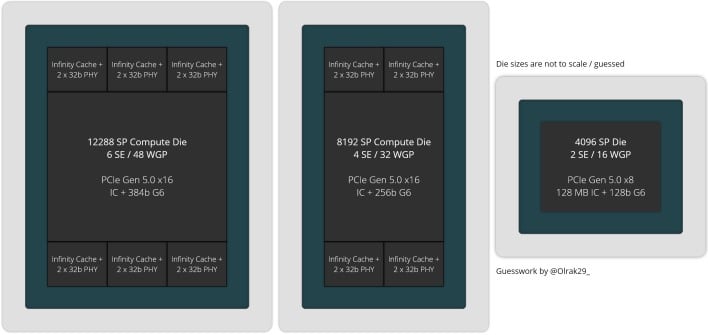

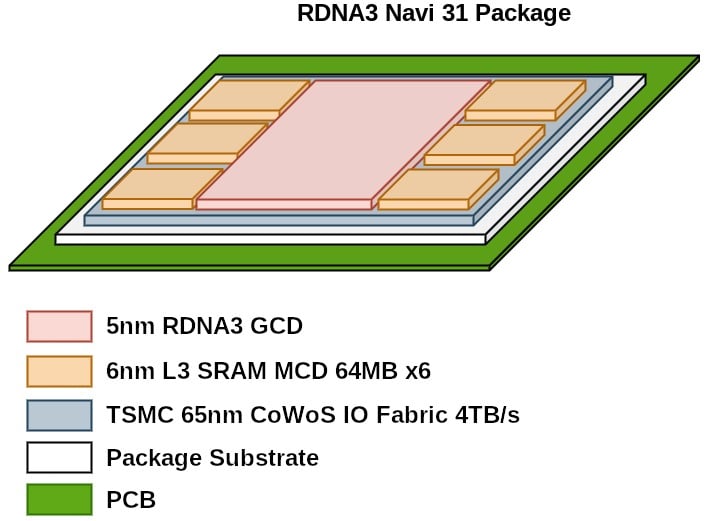

That die-area-to-price-scaling issue may be why AMD has supposedly elected to move its Infinity Cache off-die in the next generation of Radeon products. Indeed, if the latest rumors are accurate, AMD's next-generation Navi 32 and Navi 31 parts, the largest Radeon RX 7000 series GPUs, will move the Infinity Cache off-die, onto the "Memory Controller Dice" or MCDs. However, the latest rumor says that the biggest part could use as many as six MCDs.

Another reliable leaker, Moore's Law is Dead, believes that there will in fact be two GCDs (Graphics Core Dice), but that they will be vertically stacked, like 3D V-cache. This would allow both dice to work in tandem essentially like a single chip. However, given the revised numbers of resources expected in the upcoming GPUs—12288 shaders instead of 15360—it's looking a lot more likely that the GCD could be a single monolithic part itself.

Another guess at how Navi 31 will be laid out, by @AMDGPU_ on Twitter.

Notably, the latest rumor that places Navi 31 having six MCDs also implies that the biggest Radeon RX 7000 parts will come with a 384-bit memory bus. If Navi 31 were constructed like Navi 21, the news that it will include six shader engines would be enough to have us draw that conclusion. It isn't constructed that way, but purportedly it ended up with a 384-bit memory bus, anyway.

AMD's options to fill twelve 32-bit memory channels would be to use 1GB packages for 12GB of video memory, or 2GB packages for 24GB. Naturally, people have assumed that 24GB will be the total, as 12GB of video RAM is, incredibly, a bit small for a top-end GPU these days. Depending on the speed of GDDR6 that AMD selects, this configuration could offer memory bandwidth anywhere from 768 GB/sec all the way up to 1152 GB/sec, if AMD ends up using that hot-clocked GDDR6 memory that Samsung showed off last year.