RPCS3 Dev Details Huge CPU Performance Gains With AVX-512 For Beloved PS3 Emulator

Intel later included the instruction set in its 11th-generation Rocket Lake processors, only to then remove it again in the 12th-generation processors. We've written quite a bit about the saga of AVX-512 on Alder Lake, where the CPUs' P-cores support it but the E-cores don't, and as a result Intel has elected to forcibly disable the instruction set on all Alder Lake processors for whatever reasons.

A lot of people have a lot of strong feelings on AVX-512. Probably too strong, if we're honest. Linus Torvalds famously wished the instruction set a "painful death," and comments around the web (including on our own AVX-512 stories) seem to indicate that many consumers see the feature as pointless excess. Torvalds himself lamented the die area and research time that AVX-512 units occupy, wishing instead for faster general-purpose performance in lieu of the focus on 512-bit-width vectors with limited application to general-use computing.

The thing is, AVX-512 is actually rather poorly-named and marketed. Sure, the instruction set includes support for massive 512-bit-width vector math. It includes a whole lot more than that, though. People often think of AVX-512 in terms of AVX in general, where the original AVX was mostly just an extension of extant SSE instructions to support 256-bit width. To be sure, AVX-512 isn't that.

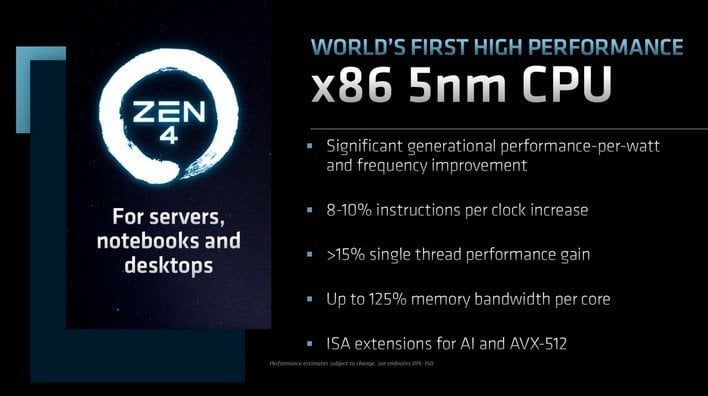

Exactly what AVX-512 *is*, however, is a more difficult question to answer, because there are no less than eighteen different categories of "AVX-512" instructions. Not only are there so many new instructions that we can't even list them all, to make matters worse, none of the CPUs with "AVX-512 support" actually support all of the types of AVX-512 instructions. Indeed, while AMD's upcoming Zen 4 CPUs will support AVX-512 in some capacity, we don't know yet exactly which instructions it will support beyond the VNNI block.

Exactly what AVX-512 *is*, however, is a more difficult question to answer, because there are no less than eighteen different categories of "AVX-512" instructions. Not only are there so many new instructions that we can't even list them all, to make matters worse, none of the CPUs with "AVX-512 support" actually support all of the types of AVX-512 instructions. Indeed, while AMD's upcoming Zen 4 CPUs will support AVX-512 in some capacity, we don't know yet exactly which instructions it will support beyond the VNNI block.

Still, even with all those instructions, you may wonder what they're good for. Well, quite a bit, as it turns out—regardless of whether you're working with 512-bit data types. One specific case that we've talked about in the past is for video game emulation. The "Dynarmic" core that translates ARM CPU functions into x86 code is used in several popular emulators, including Nintendo Switch emulator Yuzu and PlayStation Vita emulator Vita3k. It makes extensive use of AVX-512 when it's available for various significant speed-ups.

Essentially, the benefits of AVX-512 in RPCS3 come down to five things: the larger register file, new instructions, new forms of old instructions, mask register support, and then a greater ability to accommodate the PlayStation 3's idiosyncrasies. The latter point is definitely specific to RPCS3 as an application, but the first four points are qualities of CPUs equipped with AVX-512 support that can definitely benefit almost all types of applications.

Given that AMD's Zen 4 CPUs will come with some measure of AVX-512 support, and given AMD's big drive for market share in the last couple of years, we expect that Intel will have to figure out some way to support the ISA in its hybrid architecture processors—even if that means poking Microsoft and the Linux folks for further and further scheduler modifications.

Obviously, to make use of any instruction set extensions (such as AVX, SSE, or old MMX), the program has to be compiled with such support. Developers of consumer software like PC games are loathe to move to new technologies that may lock out a portion of their customer base, but given the performance gains unlocked by these instruction set extensions, it's only a matter of time before games start to make greater use of wide SIMD.

Thumbnail and top image from Wikimedia Commons.