Intel Xeon Processor E5 v4 Family Debut: Dual E5-2697 v4 With 72 Threads Tested

Xeon E5 v4 Processor Architecture

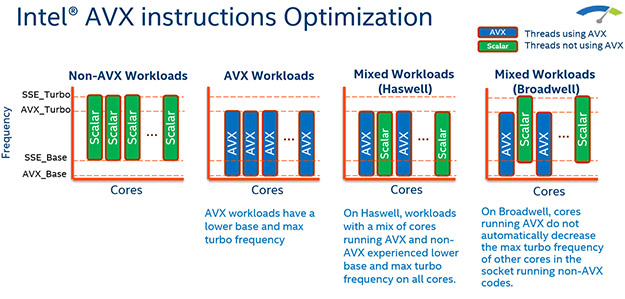

There are also enhancements to the way AVX instructions are processed, cryptography improvements, and hardware controlled power management coming with the Broadwell-EP based Xeon E5 v4 processor family.

With Haswell-EP based Xeons, executing AVX instructions resulted in all cores dropping to lower base and max turbo frequencies. And that happened with full AVX workloads or mixed scalar and AVX workloads. With Broadwell-EP, however, running AVX workloads only results in reduced frequencies on the cores actually handling the AVX workloads. With mixed scalar and AVX workloads, the cores running scalar operations do not automatically clock down. This change will result in higher overall performance for the platform when AVX is used.

New and faster data encryption and decryption and trusted compute tools available with Broadwell-EP based Xeon E5 v4 processors too. Cryptography performance improvements come by way of new instructions, like ADOX and ACDX, increased multiplier throughput, and a new Random Seed Generator (RDSEED). Multiplier throughput was essentially doubled with Broadwell-EP and RDSEED allows effective 128-bit encryption much faster than previous generation processors. On a related note, we should also mention that there are improvements to the divider in Broadwell-EP that reduces latency and improves performance too.

Another security related feature called Supervisor Mode Access Prevention (SMAP) is available with the Xeon E5 v4. SMAP is a CPU-based mechanism for User Mode address-space protection, similar to OS Guard SMEP (Supervisor Mode Execution Prevention) that prevents supervisor mode execution from user pages. SMAP helps prevent unintended supervisor mode accesses to data, though it requires OS level support.

Broadwell-EP also features Hardware Controlled Power Management, or HWPM. If you’re familiar with the Speed Shift feature introduced with Skylake, it essentially moves processor P state control from the operating system into the CPU hardware itself. The end result is that Skylake-based processors can more quickly ramp up and spool down based on the particular workload, which improves latency, responsiveness, and overall platform efficiency. The HWPM in Broadwell-EP isn’t quite as advanced as Speed Shift, but it does many similar things.

With Haswell-EP based Xeons, executing AVX instructions resulted in all cores dropping to lower base and max turbo frequencies. And that happened with full AVX workloads or mixed scalar and AVX workloads. With Broadwell-EP, however, running AVX workloads only results in reduced frequencies on the cores actually handling the AVX workloads. With mixed scalar and AVX workloads, the cores running scalar operations do not automatically clock down. This change will result in higher overall performance for the platform when AVX is used.

New and faster data encryption and decryption and trusted compute tools available with Broadwell-EP based Xeon E5 v4 processors too. Cryptography performance improvements come by way of new instructions, like ADOX and ACDX, increased multiplier throughput, and a new Random Seed Generator (RDSEED). Multiplier throughput was essentially doubled with Broadwell-EP and RDSEED allows effective 128-bit encryption much faster than previous generation processors. On a related note, we should also mention that there are improvements to the divider in Broadwell-EP that reduces latency and improves performance too.

Another security related feature called Supervisor Mode Access Prevention (SMAP) is available with the Xeon E5 v4. SMAP is a CPU-based mechanism for User Mode address-space protection, similar to OS Guard SMEP (Supervisor Mode Execution Prevention) that prevents supervisor mode execution from user pages. SMAP helps prevent unintended supervisor mode accesses to data, though it requires OS level support.

Broadwell-EP also features Hardware Controlled Power Management, or HWPM. If you’re familiar with the Speed Shift feature introduced with Skylake, it essentially moves processor P state control from the operating system into the CPU hardware itself. The end result is that Skylake-based processors can more quickly ramp up and spool down based on the particular workload, which improves latency, responsiveness, and overall platform efficiency. The HWPM in Broadwell-EP isn’t quite as advanced as Speed Shift, but it does many similar things.